Linting

What is meant by lint? It was the name originally given to a program that flagged suspicious and non-portable constructs in software programs.

Later this was extended to hardware languages as well for early design analysis. That means rule checks will be applied on the developed RTLs and it helps to identify errors which we would be getting in the upcoming design cycle stages like synthesis etc.This also helps to make sure that during optimization stage, design functionality is not changed. Overall, it points out where the code is likely to have bugs.

One important point about linting is that it checks the cleanness and portability of the HDL code for various EDA tools and not anything related to the actual functionality of the design.

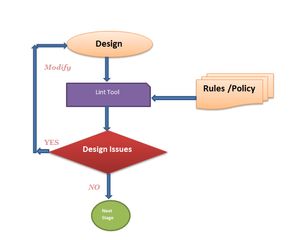

How does it work? There are some set of rules defined in the lint tool. Rule means a condition that has to be checked on your design. User can enable and disable the required rules as per his requirement. Once these rules are run on the design, and if design source code does not conform to a rule, violation will be reported.

You can have your own policy file (tcl file) specifying the rules to be checked for. Also specify whether you want particular rule check result has to be an error, warning or info.

Steps

- Change configuration/Define rule set.

- User can change the configuration settings and modify the rules set by enabling or disabling as per their requirement.

- Invoke tool and Source rules

- Analyse Design

- Elaborate

- Generate report

Areas Covered

- Differences between simulation and synthesis semantics

- Opportunities to improve simulation performance

- Probable simulation errors

- Chances of matching gate level simulations with RTL simulations

- Coding guidelines

- FSM state reachability and coding issues

- Network and connectivity checks for clocks, resets, and tri-state driven signals

- Module partitioning

- Tool flow issues in the upcoming design cycle stages

- Possible synthesis issues. (eg unintended latches or combo loops)

- Clocks and reset definitions.

Sample Rules

- COMBO_LOOP : It reports if there is a combinational loop in the design.

- TERMINAL_STATE : It reports, if a state in a FSM that once entered never reaches to another state via next state assignment.

- COMBO_NBA : It reports NBA reg assignment from a combo block.

- MULTI_DEFINES : It reports, if there are more than one macros with the same name.

- INC_SENS_LIST : If a signal is referenced and not used in the sensitivity list of the block, it reports the failure.

Tools: Some of the available tools in the market to do linting and CDC checks are

- Spyglass

- Realintent (Ascentlint, IIV,Meridian)

- LEDA

- SureLint

- Most of the formal verification tools (Onespin, IFV etc)