Metastability

Last modified 2019-01-29

Sini

In digital circuit, the signal is required to be within certain voltage or current limits (logic 0/1 levels) for correct circuit operation. If the signal is within an intermediate range other than acceptable 0/1 levels, the logic gates' behaviour will be faulty. The circuit is in metastable state when it is unable to settle into a stable “0” or “1” within an acceptable time for proper circuit operation. This may lead to system failures.

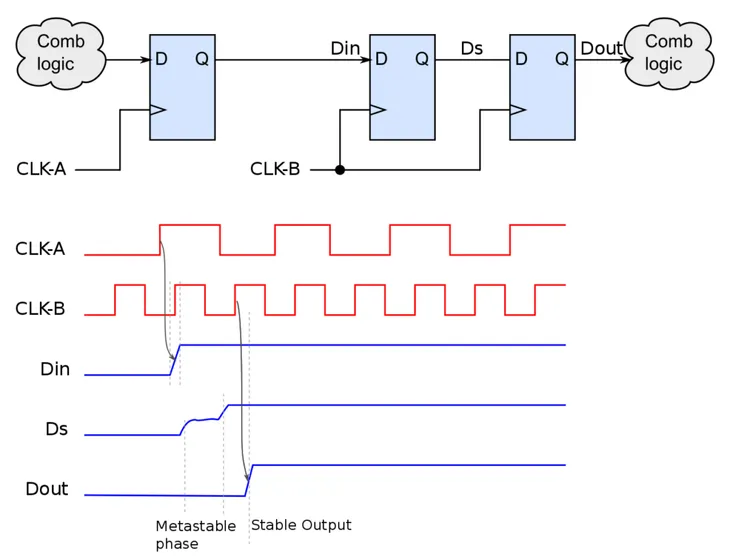

Let's confine to the metastability occurring in synchronous circuits in this article. If we could ensure that there is no setup or hold violations in the design, and all the data is latched through a clock with enough time for stable operation, metastability would not occur. However, there will be asynchronous data signals to the flop, and it is almost impossible to ensure in a big design that it will not reach the data pin in the setup/hold range of the flip flop with respect to the clock edge for some scenarios. Consider a path is violating the setup time of a flop. i.e.the data is changing in the Ts window of the capture flop. The output of the capture flop will be in an indeterminate state between the previous and old value for sometime, before eventually settling into one value(Either the previous value or the new value). Theoretically the indeterminate state can be of infinite duration, but the probability of settling into one value becomes greater as the time increases. If the device hasn't resolved the metastability in the time available for the next stage operation, this is called a 'metastability failure'. There are a few common scenarios where you need to take into account the possibility of the circuit going into metastable states.

1. Asynchronous inputs like resets. 2. Clock domain crossing – When data signals are crossing from one clock domain to another, synchronization of the data with respect to the capture clock is difficult to achieve. 3. Timing violations due to clock skew or path delays

[caption id="attachment1882" align="alignleft" width="1000"]

Next Post 1. Synchronizers 2. MTBF