Two Stage Synchonizers

Last modified 2019-02-05

Sini

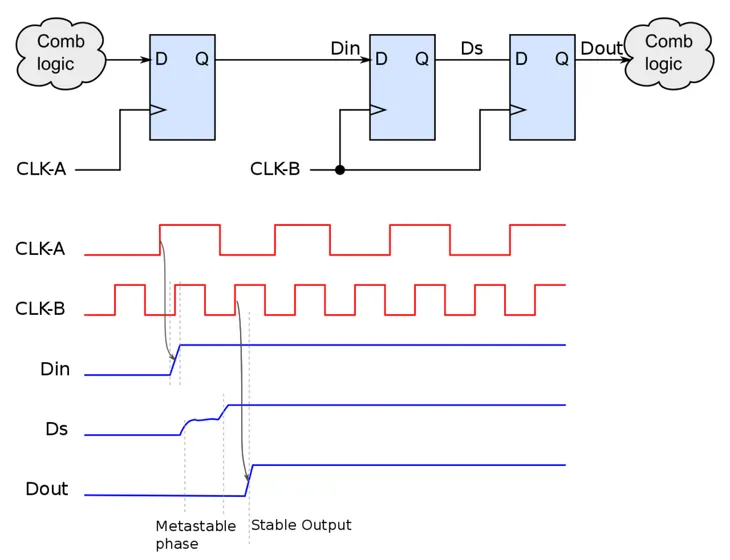

When an asynchronous signal, or a signal from a block clocked by a different clock is received by a synchronous circuit, it is imperative that it is reliably sampled by the receiver. Since the signal is asynchronous to the receiver in these cases, a special circuitry named synchronizer is used to ensure proper sampling and synchornization with respect to the receiving clock. If the data changes in an unacceptable range of the clock, metastability occurs as explained previously. This can be avoided by giving enough time for the meta stable output to settle down. The most common method used is the two stage synchronizer using flops.

[caption id="attachment1882" align="alignleft" width="1000"]

The two flops should be placed as close to each other as possible so there is no combinational delay between the flops. This ensures that entire clock cycle is available for the metastability to resolve. There is a possibility that the input will be settled into a wrong value, and this wrong input will be propagated to the subsequent stages. It is important that the input from one domain stays stable for at least one clock cycle so that the wrong stable data(after a metastability event) is not propagated. The disadvantage in using these synchronizers are the overhead it adds in propagation delay, area and power. Special synchronization flops are available in your libraries which have higher value of MTBF, and is specially designed for reducing the failure rate.

MTBF Metastability failures are probablisitic in nature. You cannot avoid metstability, but MTBF or the Mean Time Between Failures gives you a measure to determine the reliability of the device with respect to metastability failures. It gives the avergae time betwen two failures for the device.