Clock Jitter

Last modified 2013-10-19

Sini

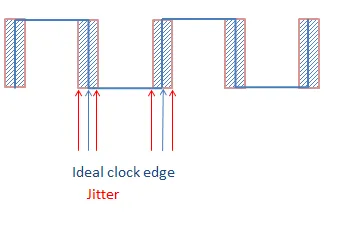

In the article Clock Uncertainty I mentioned that the command setclockuncertainty is used to account for among other things, clock jitter. Clock jitter is a characteristic of the clock source and the clock signal environment. It can be defined as "deviation of a clock edge from its ideal location." Clock jitter is typically caused by clock generator circuitry, noise, power supply variations, interference from nearby circuitry etc. Jitter is a contributing factor to the design margin specified for timing closure.

-

Period jitter Period jitter is the deviation in cycle time of a clock signal with respect to the ideal period over a number of randomly selected cycles(say 10K cycles). It can be specified an average value of of clock period deviation over the selected cycles(RMS value) or can be the difference between maximum deviation & minimum deviation within the selected group(peak-to-peak period jitter).

-

Cycle to cycle jitter C2C is the deviation in cycle of of two adjacent clock cycles over a random number of clock cycles. (say 10K). This is typically reported as a peak value within the random group.This is used to determine the high frequency jitter.

-

Phase jitter In frequency domain, the effect being measured is phase noise. It is the frequency domain representation of rapid, short-term, random fluctuations in the phase of a waveform. This can be translated to jitter values for use in digital design.

Please note all the above jitters are effectively the same phenomenon, but different way of measuring and representing the effect for use in design flow. The jitter number thus obtained is used to specify the design margin using the command "setclockuncertainty".

Effects

Since the jitter affects the clock delay of the circuit and the time the clock is available at sync points, setup and hold of the path elements are affected by it. Depending on whether the jitter causes to clock to be slower or faster, there can be setup hold or setup violations in an otherwise timing clean system. This will in turn lead to performance or functional issues for the chip. So it is necessary that the designer knows the jitter values of the clock signal and account for it while analyzing timing.