Common Path & Clock Reconvergence Pessimism Removal

Last modified 2018-05-10

Sini

Many a time your chip is overdesigned due to undue pessimism in timing calculations. Pessimism in timing analysis makes it difficult for designs to close timing and it is imperative that analysis is not overly pessimistic. There is a clock path related pessimism observed in timing calculated in on-chip-variation mode, and EDA tools have the capability to automatically remove the pessimism while analysis.

Common Path Pessimism Removal (CPPR)

A timing path consists of launch and capture paths. The launch path has further components – the launch clock path and the data path.

c1->c2->c3 -> CP-to-Q of FF1 -> c5 -> FF2/D

The capture path is c1->c2->c4->FF2/CP

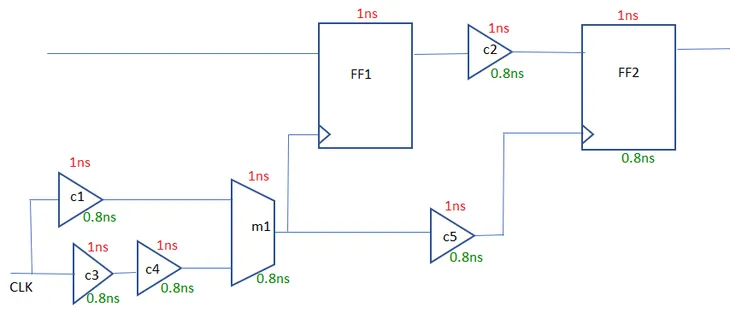

Late and early derates are set for cells and nets while doing timing analysis in on-chip-variation mode. For setup analysis, STA tool does late check for launch clock path and the data path, and early check for the capture clock path. However, part of both capture and launch clock paths are same, till node n1. In the image given, numbers in red denote the max delays(late delay numbers) and numbers in green are min delays(early delay numbers). Let us assume the net delays are included in the numbers.

For setup analysis, the launch clock path delay is: c1->c2->c3 ->FF1/CP ==> 1ns+1ns+1ns+ = 3ns The capture clock path delay is c1->c2->c4->FF2/CP ==> 0.8ns+0.8ns+0.8ns = 2.4ns

However, part of the clock paths is common, till node n1. It is not realistic that these have two different delays for the same analysis. Using the late and early timing numbers for the common path creates unwanted pessimism in timing analysis leading to difficulties in timing closure or overdesign. Hence removal of this pessimism is necessary. For the example noted above we can see a “CPPR adjustment” of 0.4, i.e. the skew between the clock paths will be 0.2ns, instead of 0.6ns. + CPPR Adjustment 0.4

Different PD and STA tools have various attributes to selectively enable clock path pessimism removal.

Clock Reconvergence Pessimism

In some case clocks reconverge after taking different paths. In the circuit given below, the clock splits into two different combinational logic before converging through mux m1.

The clock convergent point in m1/Y. Launch clock till convergence: c3->c4->m1 ==> 1ns+1ns+1ns = 3ns

Capture clock till m1/Y: c1->m1 ==> 0.8ns+0.8ns = 1.6ns

Clock reconvergence pessimism: 1.4ns