Clock Groups : set_clock_groups

Last modified 2019-02-06

Sini

Table of content

Back when I gave an introduction to SDC, I brushed upon `setfalsepath` statements between clocks. However, now there is a more efficient way of specifying the the clock exceptions in the design. `setclockgroups` is a powerful way of letting the P&R and STA tools know what is expected of it during optimization and analysis.

There are three options to this command. `-asynchronous`, `-logicallyexclusive` and `-physicallyexclusive`. Let's tackle them one by one.

Asynchronous Clocks

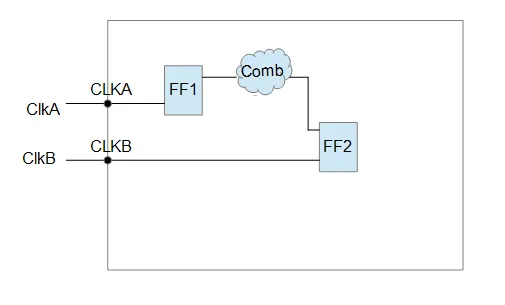

`setclockgroups -asynchronous` When you say two(or more) clocks are asynchronous, that means there is no phase relationship between them at all. Consider the following statements:

`createclock -period 10 -name ClkA [getports CLKA]` `createclock -period 1- -name ClkB [getports CLKB]`

This is equivalent to setting the following two false path statements. `setfalsepath -from [getclocks ClkA] -to [getclocks ClkB]` `setfalsepath -from [getclocks ClkB] -to [getclocks ClkA]`

Case 1

`setclockgroups -asynchronous -group {ClkA ClkC} -group {ClkB ClkD}`

Breaking down the above command gives us-- 1. ClkA and ClkC are synchronous to each other. 2. ClkB and ClkD are synchronous to each other. 3. ClkA & ClkC are asynchrnous to ClkB & ClkD and vice versa. i.e. The members of a group are synchronous to each other, but asynchronous the to the elements in the other group.

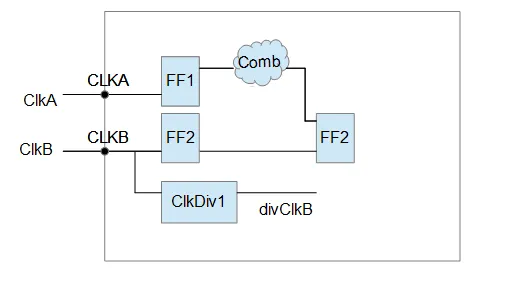

Case2 Now, consider that one(or both) of these clocks generated other clock, say by a clock divider as in the figure below.

Logically Exclusive Clocks

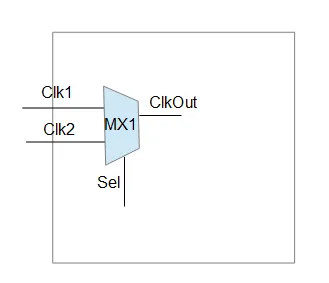

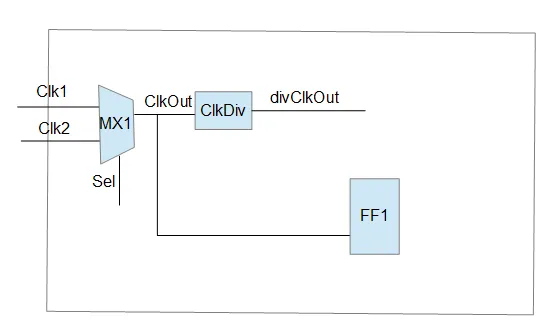

Two clocks are said to be logically exclusive when they are both active in the design but doesn't have any paths between them. An example would be a MUX selecting two or more of the clocks for a portion of the design using its select lines. Such clocks will not have any timing path between them. Let's see the circuit below:

Case1 The clock clkOut is selected by the Sel line of the Mux MX1. So, Clk1 and Clk2 cannot exist together logically in the downstream path of the MX1. They are not interacting outside the MUX path.

`setclockgroups -logicallyexclusive -group [getclocks Clk1] -group [getclocks Clk2]`

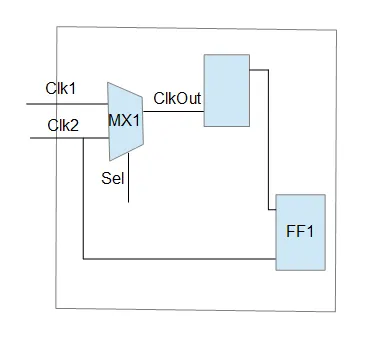

Case2 There is logic on Clk2 outside the MUX which is interacting with flops clocked by ClkOut, we cannot specify a logicalexclusion on Clk1 and Clk2. What you can do here is create generated clock statement for the output of the MX1.

`creategeneratedclk -name genClk1 -source MX1/Y -master Clk1` `creategeneratedclk -name genClk2 -source MX1/Y -master Clk2` `setclockgroups -logicallyexclusive -group [getclocks genClk1] -group [genClk2]`

Case 3 There is a clock divier on ClkOut. In such cases you need to create two generated clock statements for this with Clk1 & Clk2 as the master clock.

`creategeneratedclk -name genDivClk1 -source ClkDiv/Y -master Clk1` `creategeneratedclk -name genDivClk2 -source ClkDiv/Y -master Clk2` `setclockgroups -logicallyexclusive -group [getclocks {Clk1 genDivClk1}] -group [getclocks {Clk2 genDivClk2}]`

Physically Exclusive Clocks

These clocks do not exist in the design at the same time. e.g. Clocks defined on the same primary port but working in two different modes like the TestClk and Functional Clock. There will be no SI interaction between these clocks.

`setclockgroups -physicallyexclusive -group [getclocks TestClk] -group [getclocks SysClk]`